锁相环 PLL

在射頻與高速時脈系統中,頻率穩定度、相位雜訊與時序一致性,往往直接影響整體電路表現。當設計需要完成頻率合成、時鐘重整、訊號同步或本地振盪控制時,鎖相環 PLL 相關元件便是相當核心的一環。對工程採購、硬體設計與系統整合人員而言,選擇合適的 PLL 裝置,不只是比對頻率範圍,還需要同時考量輸入輸出介面、供電條件、封裝形式與應用場景。

PLL 在射頻與時鐘架構中的角色

鎖相環 的核心用途,是讓輸出訊號在頻率與相位上追隨參考訊號,進一步完成倍頻、分頻、頻率合成或抖動改善等功能。在實際設計中,它經常出現在通訊設備、時鐘分配、高速資料傳輸、嵌入式控制與各類需要精準同步的電子系統。

在更完整的射頻訊號鏈裡,PLL 也常與其他元件搭配使用。例如在本地振盪與頻率轉換架構中,會與上變頻器和下變頻器共同構成關鍵功能模組;若是面向無線收發設計,也常延伸到射頻前端的整體頻率規劃。

這個類別常見的器件型態

雖然頁面主題聚焦於 PLL,但實務上相關需求通常會延伸到時鐘發生器、頻率合成器、抖動衰減器,以及具 PLL 架構的時脈元件。這些產品在功能上彼此關聯,差異主要來自是否強調可編程輸出、輸出通道數、抖動控制能力,或是否針對高速介面最佳化。

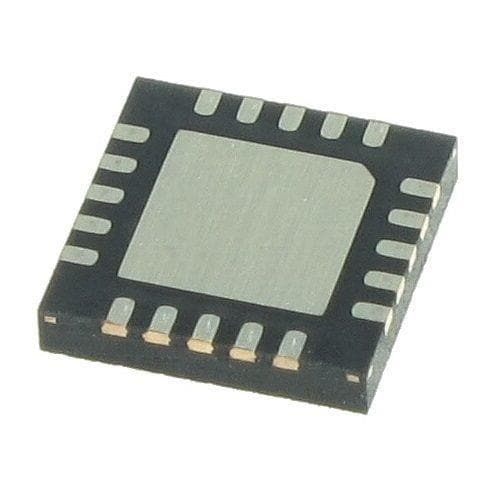

以頁面中的代表產品來看,Microchip DSC612PA3A-01EQ 屬於 PLL 時鐘發生器,適合需要小型封裝與寬供電範圍的設計;Infineon CY22150FZXI 則偏向可編程時鐘發生器,適用於多輸出時鐘配置;像 Microchip PL611-01-F93TC-R 這類頻率合成器,則更適合需要依參考源建立目標頻率的應用。若系統對時序品質更敏感,時鐘抖動衰減器也會成為設計重點。

選擇鎖相環 PLL 時應優先看的幾個條件

第一個關鍵通常是頻率範圍。不同應用對輸出頻率需求差異很大,從 kHz 等級的基礎控制訊號,到數百 MHz 甚至更高的高速時鐘都很常見。若系統涉及 SerDes、通訊同步或高頻資料路徑,輸出上限、頻率解析度與穩定性就特別重要。

第二是輸入與輸出介面類型,例如 CMOS、LVCMOS、LVDS、LVPECL、HCSL 或 ECL。這些介面不僅關係到訊號相容性,也會影響 PCB 佈線、終端匹配與電磁干擾控制。像 Microchip PL903167UMG TR 支援多種輸出型態,適合需要介接不同時脈架構的系統;onsemi MC100EP139DTR2G 則更適合特定高速邏輯環境。

第三是供電與封裝條件。工業與嵌入式系統常受限於板面空間、電源架構與熱設計,因此從 SOT-23、TSSOP 到 QFN-EP、VFLGA 等封裝,都會影響整合方式。若應用涉及車用或較寬溫環境,也應同步檢查工作溫度與是否具備對應等級,例如頁面中的部分型號可支援至 125 °C,較適合高可靠度場景。

抖動、同步與訊號品質的重要性

PLL 類元件不只是「產生一個頻率」而已。在高速數位與通訊系統中,抖動控制 往往比單純的頻率數值更值得關注。若時脈品質不穩,可能導致取樣誤差、位元錯判、鏈路不穩定,甚至影響整個系統的同步能力。

例如 Microchip PL902165USY 與 PL902167USY 都屬於時鐘抖動衰減器,適合用在需要改善時脈品質的情境。若設計重點放在多個模組間的時間一致性,則應進一步評估輸出數量、時序分配與參考源品質。對於需要更高頻率輸出能力的架構,像 Microchip ZL30791LFG7 這類時鐘發生器與合成器,也能提供更寬的應用彈性。

不同品牌在應用選型上的參考方向

就供應面與設計習慣來看,Microchip 在這類時鐘與 PLL 相關器件中提供多種形式,涵蓋 PLL 時鐘發生器、頻率合成器、抖動衰減器與振盪器,適合需要從基礎時脈到進階同步方案一次評估的專案。若需求偏向可編程時鐘配置,Infineon 也有對應選項可供比較。

Diodes Incorporated 在時鐘發生器與合成器方面亦常見於一般電子與嵌入式設計,例如 PI6CG33201CZDIEX、PI6CG33402CZHIEX-13R 可作為選型參考。另一方面,onsemi 的部分型號則較適合特定輸出邏輯需求。若您正在規劃更完整的射頻鏈路,也可以搭配查看耦合器等相關類別,以便更全面評估系統架構。

適用場景與採購評估方式

PLL 相關元件常見於通訊設備、工業控制板、時鐘同步模組、資料擷取系統、網通設備與需要頻率參考的射頻電路。若是多板卡或多模組系統,通常會更重視參考時鐘一致性與分配架構;若是空間受限的小型設備,則封裝與低功耗表現會更受重視。

從採購角度來看,建議先確認實際需求是偏向「產生時鐘」、「合成目標頻率」、「改善抖動」,還是「建立可編程時脈架構」。接著再比對輸出數量、介面型式、電壓範圍與工作溫度。這樣的篩選方式,通常比單看型號名稱更有效率,也更能避免後續整合時出現介面不匹配的問題。

選擇合適 PLL 元件,重點在系統匹配

面對不同的射頻與高速數位設計需求,PLL 類產品的價值在於協助系統建立穩定、可控制且可擴充的時脈基礎。無論是偏向簡潔的小型 PLL 時鐘發生器,或是支援更高頻率與多種輸出格式的時鐘合成方案,真正重要的都是與整體架構的匹配程度。

如果您正在為新專案或既有設備升級尋找合適的鎖相環 PLL 元件,建議從頻率需求、抖動表現、輸出介面與環境條件四個方向交叉評估。透過這種方式,更容易快速縮小範圍,找到適合實際應用的器件組合。

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-